|

SIFA - Bottom Up Evaluation Step 1 |

Import VHDL into SIFA. Rename the top-level "Entities" view to give the device a sensible name.

To successfully import a VHDL model into SIFA, the converter vhdl2sifa must be executed. The file input.prop specifies the command used to invoke the conversion utility, and by default contains an entry for files with the extension "vhd" and "vhdl". The default distribution of SIFA is set up such that a vhdl file opened by invoking Project->Open or Component->Import will be converted so long as "java -jar vhdl2sifa/vhdl2sifa.jar" is executable. This requires that Java version 5 be in the PATH environment. If this is not the case, the conversion will fail.

If the conversion fails for this reason, there are two possible remedies. Either edit the input.prop file to point to a command that actually will execute Java 5, or perform the conversion process manually by running "java -jar vhdl2sifa/vhdl2sifa.jar" from the command line. All conversion utilies work by transforming standard input to standard output.

If the conversion process fails for some other reason, try to interpret the diagnostic messages given in the error dialog box and alter the VHDL accordingly. If you are keen, edit the source code for the converter to make it work for your VHDL and submit the changes back to us! (Note: it might be a good idea to check out the grammar for the converter to see why your VHDL isn't parsing. It is contained in the file VhdlParserCore.jj).

When the VHDL is imported it creates a tree with a recursive structure, which maps to the structure of the VHDL specification.

For example, the following VHDL:

Library IEEE;

Use IEEE.std_logic_1164.all;

entity Example is

begin

end Example;

architecture structure of Example is

component CMP

port

(

p1,p2 : in STD_LOGIC;

p3,p4 : out STD_LOGIC

);

end component;

signal sig1, sig2 : STD_LOGIC;

begin

instance1 : CMP

port map

(

p3 => sig2,

p4 => sig1

);

instance2 : CMP

port map

(

p1 => sig1,

p2 => sig2

);

end structure;

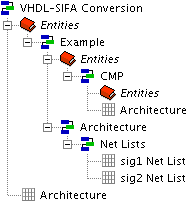

Is imported into the following structure:

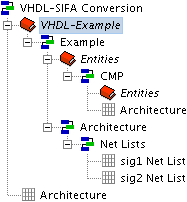

Our example device has two instances of a component "CMP" that are connected serially by the signals "sig1" and "sig2". The top-level entity in the VHDL in this case is "Example", and we are free to use that in SIFA immediately. However, the top-level of the VHDL might describe an architecture without encapsulating it in this way (using a single component). If that is what we wish to instantiate, we must rename "Entities" to something meaningful so we use the entire definition when we reference it. In this case, I'll use the name VHDL-Example, even though it isn't particularly helpful for such a simple system ("Example" and "VHDL-Example" are equivalent).

In fact, "Entities" must be renamed in most cases because that name is overloaded in the imported model — it appears three times in the example above. This overloading will have a significantly adverse effect on the analysis if "Entities" is instantiated.

Note: The example presented here closely resembles the example in the user guide where consistency analysis is discussed.